.png) DDR介面

DDR介面

從低中速傳輸頻寬到高速傳輸頻寬和Low Power,本公司提供各種工藝的多樣的DDR介面、巨集。另外通過使用Chip-Package-Board協調設計的設計支援,我們支援客製化Soc開發。

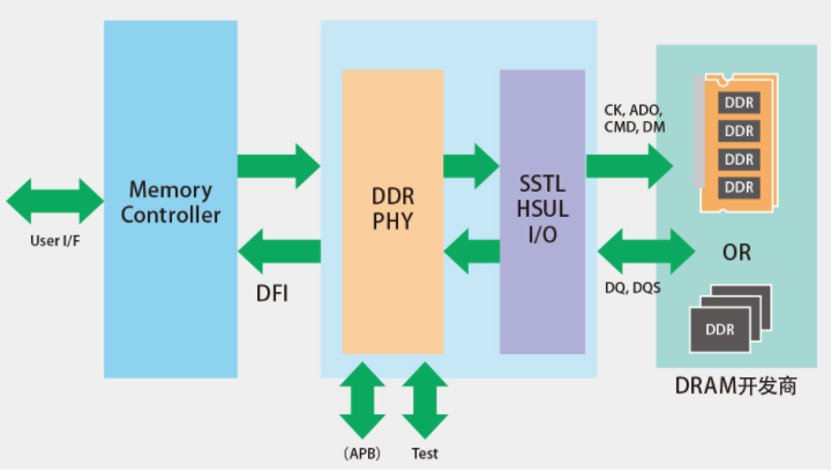

[DDR介面結構圖]

●DDR介面、巨集

- 高速/高頻寬(高速宏):DDR3/DDR4

- Low Power(低功耗宏):LPDDR4X/4/3/2DDR3L

- 遵守DFI(所有宏)

- 通過PHY功能(Training功能),支持Fly-by、PoP、DIMM、etc. 多樣的DRAM配置、PKG選項

●支援DDR介面設計(Chip–Package–Board 協調設計)

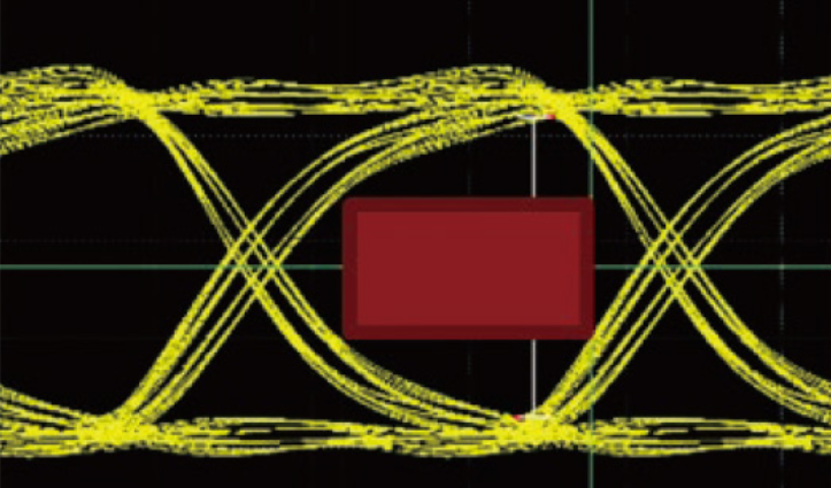

- Timing驗證:驗證包括 LSI.I/O ~ DRAM間延遲的DDR- IF整個系列的Timing

- Power Integrity:作為 電源 Impedance設計優化寄存電感、共振頻率、電源(PKG,PCB)阻抗

- Signal Integrity:Driver Strength、終端電阻、佈線Topology的優化

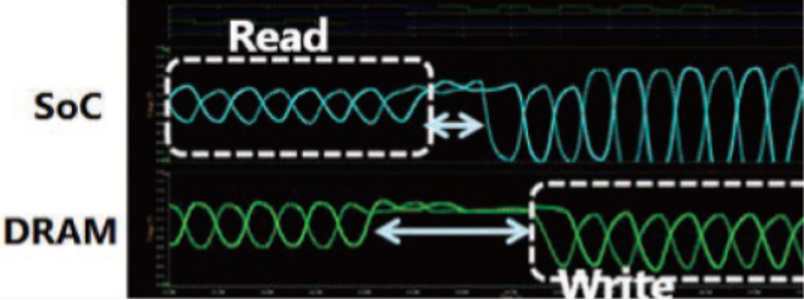

- 匯流排切換驗證:寫入/讀取匯流排切換時機的最優化

[LPDDR4-3733 DQ 波形]

[匯流排切換波形]

.png) 記憶體控制器

記憶體控制器

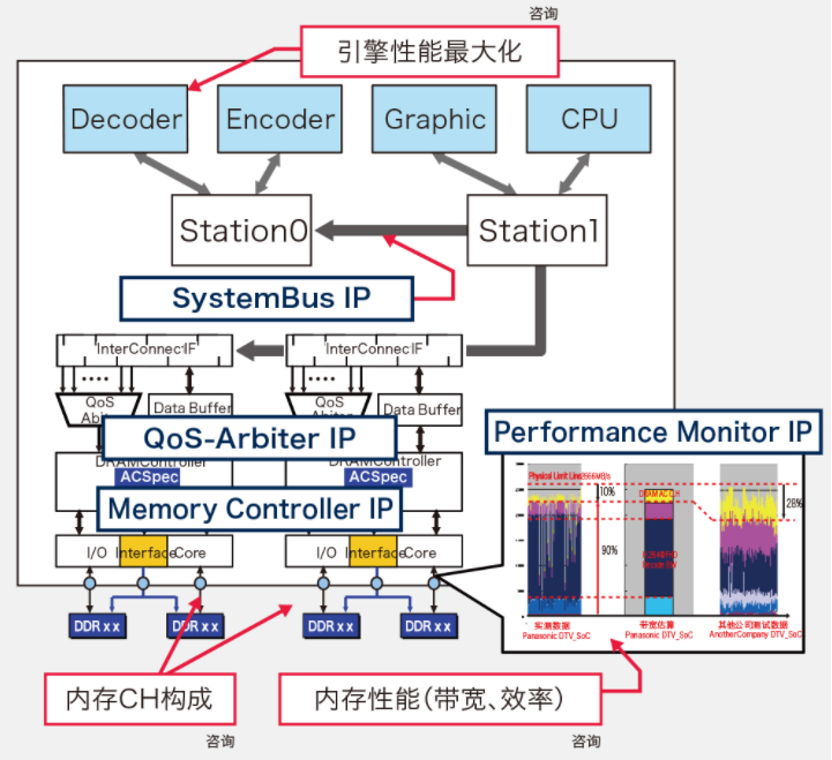

我們為優化系統提供各種記憶體的解決方案。另外在記憶體通道、系統匯流排方面,進行記憶體系統的諮詢來提升客戶的SoC性能。

●記憶體控制器IP

- 提高DRAM使用率的控制器

●QoS-判優器IP

- 高性能、高功能的多功能QoS -判優器

●BusIP

- 低功耗佈局靈活性高的獨創匯流排

●MonitorIP

- 即時顯示記憶體系統性能

監控性能(頻寬、Latency),提供調諧參數環境。

.png) MIPI 介面

MIPI 介面

用於搭建與高速、高解析度的CMOS圖像感測器相連的相機及顯示器系統的高速介面。提供可實現高度影像表現力的解決方案。

●MIPI D-PHY TX 宏

最高速度4.5Gbps,小面積的高性能宏

- 4Data Lane+1Clock Lane 結構

- 傳送速度:80Mbps ~ 4.5Gbps@1lane

- 等化器功能

- 實現世界最小級別的面積

- 支持D-PHY2.0

[D-PHY TX 輸出波形@4.5Gbps]

.png) PCI Express介面

PCI Express介面

隨著近些年CPU處理能力的飛躍性提高和大容量資料傳送需求的擴大,以現有的匯流排實現使用者期待的系統性能已變得非常困難。為了解決此課題,可傳送幾百百萬位元組資料的高速介面採用了PCI Express技術。

我公司的PCI Express 宏是最高可支援8GT/s(Gen3),通過了PCI-SIG 主持的PCI Express 標準的合規測試,並且已確認了與多數PCI Express介面的互聯性和可靠性。

[PCI Express Gen3 評估環境]

●PCI Express LINK宏

- 遵循標準規格PCI Express Base Specification rev.3.0

- 支持lane 數×1/×4/×8

- DualMode(RootComplex/Endpoint可選)

- 使用者介面可選擇AMBA3 I/F

- 搭載內置DMAC

●PCI Express PHY宏

- 最大比特傳送率64GT/s

- 通過De-emphasis功能保證高速信號傳輸

- LINK巨集介面遵循標準規格PIPE3/PIPE4

.png) 10G–28Gbps SerDes介面

10G–28Gbps SerDes介面

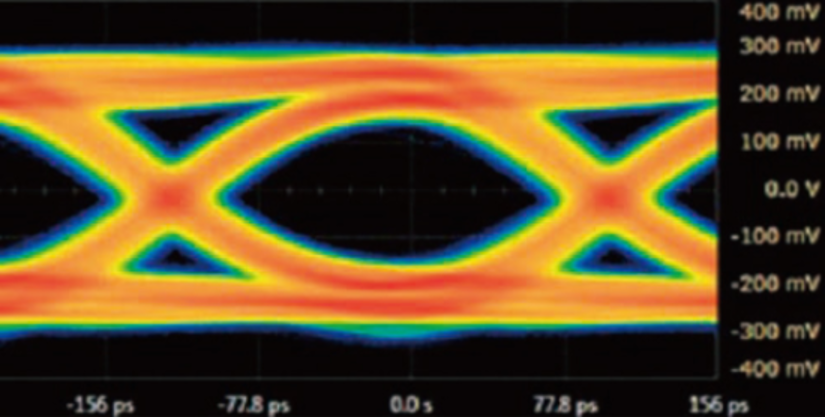

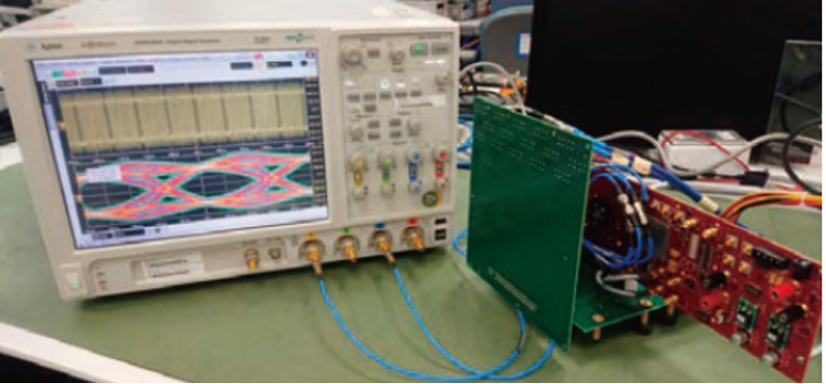

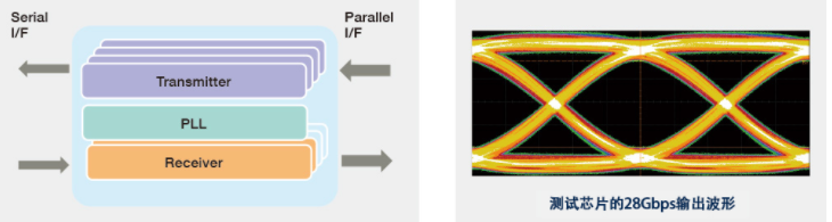

每個通道具備10 Gbps〜28 Gbps的傳輸性能,通過組成多個通道,我公司可以提供用於構建100 G/200 G/400 G的Optical network和100 G Ether系統的高性能SERDES巨集。

通過內置低抖動的高性能PLL,可實現每個通道最大28 Gbps的強大的傳輸功能。支持OIF-CEI-11G-SR, OIF-CEI-28G-SR, OIF-CEI-28GVSR,IEEE802.3ba CAUI, IEEE802.3bm CAUI4, XFI等各種規格。

●特點

- x1, x4LANE構成

- 由Transmitter/Receier/PLL組成,一個宏可進行雙向通信

- 每個宏最大112.8 Gbps(單向,x4構成時)

- 支援每個LANE的斷電控制

- 支援宏整體斷電控制

- 帶有各個Receiver lane的Clock-Data recovery

- 支持Transmitter Equalization

- 支持Receiver Equalization

- 在Transmitter/Receiver內置終端電阻

- 有機倒裝晶片封裝(0.8 mm/1.0 mm Ball Pitch, HDBU Package)

聯絡我們

聯絡我們