作為客戶的SoC開發環境,Socionext將借助標準EDA工具的開發環境和設計高效化的Socionext開發工具,以設計套件方式提供給客戶,並提供相應的支援。該前端設計套件是Socionext獨創優化的,可在短時間內實現高性能、小尺寸、低功耗的LSI的開發。

|

[前端設計套件支援EDA工具] |

||

|

高位綜合 |

Catapult*3, C-to-Silicon Compiler*1, Stratus*1 |

|

|

RTL 樣式檢驗 |

SpyGlass*2 |

|

|

功能驗證 |

Verilog-HDL |

Incisive Enterprise Simulator*1, Questa*3, VCS-MX,VCS*2 |

|

VHDL |

Incisive Enterprise Simulator*1, Questa*3, VCS-MX*2 |

|

|

CPF/UPF |

Incisive Enterprise Simulator-XL*1, Questa*3, VCS-NLP*2 |

|

|

邏輯綜合 |

Design Compiler*2, Encounter RTL Compiler*1, Genus Synthesis Solution*1 |

|

|

等價驗證 |

Encounter Conformal Equivalence Checker*1, Formality*2 |

|

|

時序制約驗證 |

Encounter Conformal Constraint Designer*1, SpyGlass Constraints*2 |

|

|

MV 驗證 |

Encounter Conformal Lowpower*1, VC Static Low Power*2 |

|

|

解析・調試器 |

Verdi*2 |

|

|

Netlist檢驗*4 |

SpyGlass*2 |

|

|

Pre DFT檢驗*4 |

SpyGlass DFT*2 |

|

*1:日本Cadence Design Systems公司

*2:日本Synopsys合同會社

*3:Mentor Graphics Japan株式會社

*4:依據不同工藝提供自製的檢驗工具

.png) 設計規格I/F

設計規格I/F

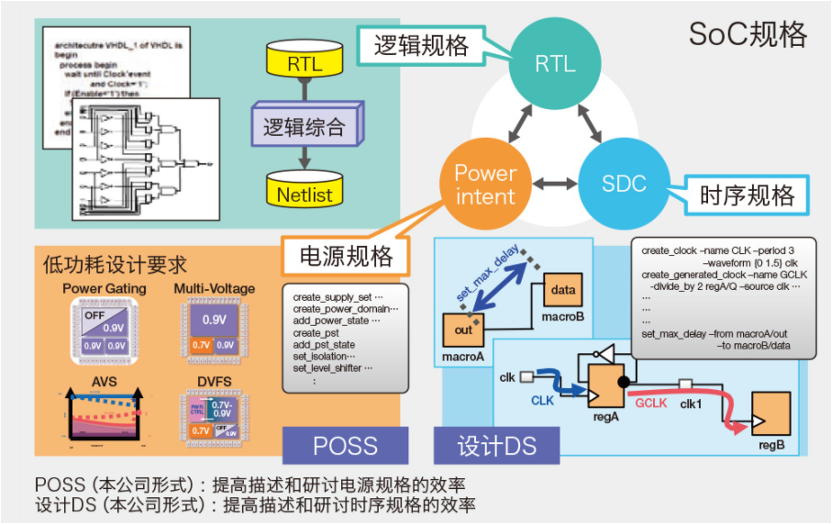

在SoC設計中,不單需要邏輯設計資料的RTL和Netlist,還需要描述了時鐘頻率等時序規格的SDC、描述電源門控設計、多電源多電壓設計等電源規格的CPU/UPF之類的Power Intent。Socionext為上述SDC和Power Intent備有獨家形式的I/F檔。通過利用這些I/F檔,可以提高描述和研討各種規格的效率,同時也可迅速驗證切換了的RTL、電源規格、時序規格的一致性、佈局的親和力等。

.png) 物理考慮邏輯綜合

物理考慮邏輯綜合

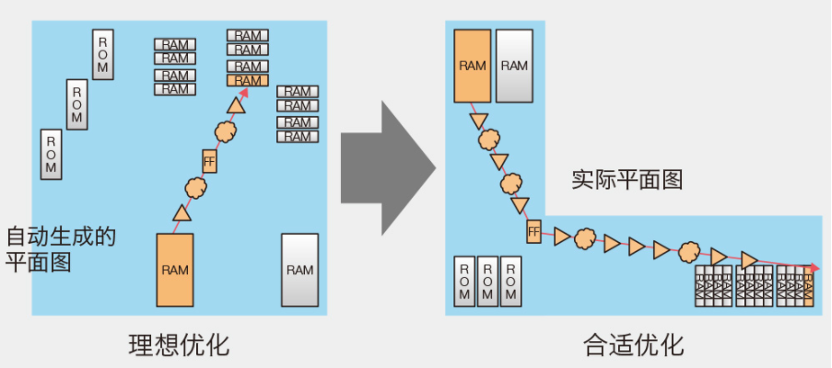

隨著技術小型化,就提高SoC設計效率和優化面積和時序而言,考慮到佈局的邏輯設計日漸變得重要。

因此,Socionext採用了物理考慮綜合方式,在進行邏輯綜合時,考慮實際佈局以進行優化。由於協調了邏輯設計和佈局設計,Socionext能夠有效率地設計高性能SoC。

聯絡我們

聯絡我們