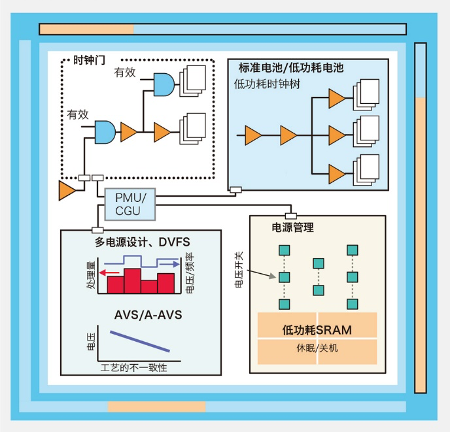

近年來,降低LSI功耗的需求越來越高。Socionext的SoC設計,為了滿足客戶對低功耗的需求,採取了各種措施。為了實現低功耗LSI,不能僅靠個別技術,而是須要綜合各種技術才會有效。在Socionext的設計環境“參考設計流程”中,支援各種低功耗技術, LSI運作時和待機時均可以降低功耗。特別是針對以控制電源方式實現低功耗化的手法進行了體系化的開發。另外Socionext通過全面採用UPF/CPF,減少對客戶資產的設計變更,使低功耗設計變得更加容易。並且通過採用UPF/CPF,對過去驗證難度很高的低功耗技術也能進行高可靠性設計。

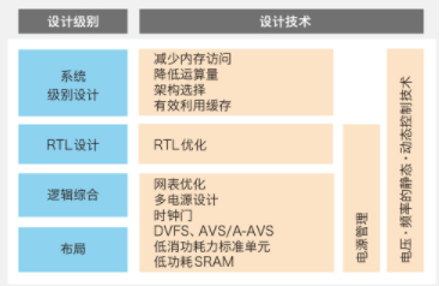

[低消功耗力化技術]

.png) 多電源設計

多電源設計

[多電源設計技術]

通過在LSI內供給不同電壓的技術,對高速運行的電路模組提供高電壓,對低速運行的電路塊提供低電壓,降低運行時的功耗量。

通過採用UPF/CPF,使不同電壓的電路模組可以進行一次性物理設計·驗證,通過這種方式可以最大程度減少由於低功耗設計引起的開發週期的增加。

.png) 時鐘門

時鐘門

通過停止不運行的電路模組的時鐘,可降低LSI運行時的功耗總量。

.png) 電源管理

電源管理

提供統一電力門控和SRAM睡眠、關機模式的電源管理。徹底排除損耗,提高低功耗化。Socionext電源管理技術,採用獨創的電源開關控制方式,抑制了供電開關切換時產生的電源雜訊,避免LSI的誤運行。

而且通過採用UPF/CPF,包括電源切斷電路模組,可以一併進行性物理設計·驗證,儘量抑制開發週期的增加。

.png) 適應性電源控制(DVFS*1、AVS*2/Advanced-AVS)

適應性電源控制(DVFS*1、AVS*2/Advanced-AVS)

支援根據需求處理量改變電壓和頻率的DVFS。同時根據製造偏差確定相應的運行電壓,通過在保證LSI運行的最低電壓下運行,可降低運行時和待機時的功耗。

*1:DVFS(Dynamic Voltage Frequency Scaling)

*2:AVS(Adaptive Voltage Scaling)

.png) 標準單元

標準單元

採用最先進的技術,不僅是標準單元的面積,佈線性也對LSI低功耗化做出貢獻。我們提供Socionext獨創設計的淩駕於其他公司產品的標準單元。還擴充了對時鐘系的低功耗化有效的單元的陣容。

.png) 低功耗SRAM

低功耗SRAM

搭載了大容量SRAM的LSI可能會出現SRAM的功耗問題。在這種情況下,通過使用多模式SRAM可降低功耗量。在多模式SRAM,除了通常運行模式外,還有待機模式、休眠模式和關機模式。在待機模式,通過停止SRAM巨集內部的時鐘運行,可使SRAM巨集的動態電為0。在休眠模式,通過將SRAM巨集的周邊電路置於非啟動狀態,可降低漏電。在關機模式可通過SRAM獨立切斷電源。另外使用SRAM結構優化也有助於低功耗化。從邏輯設計階段開始支援客戶選擇最佳的SRAM。

|

運行方式 |

功能 |

效果 |

|

通常運行 |

通常的RAM運行 |

- |

|

備用 |

運行停止 |

運行功耗為0 |

|

休眠 |

資料保存 |

漏電約為1/3* |

|

關機 |

SRAM獨立切斷電源 |

漏電約為1/6* |

*:取決於SRAM配置

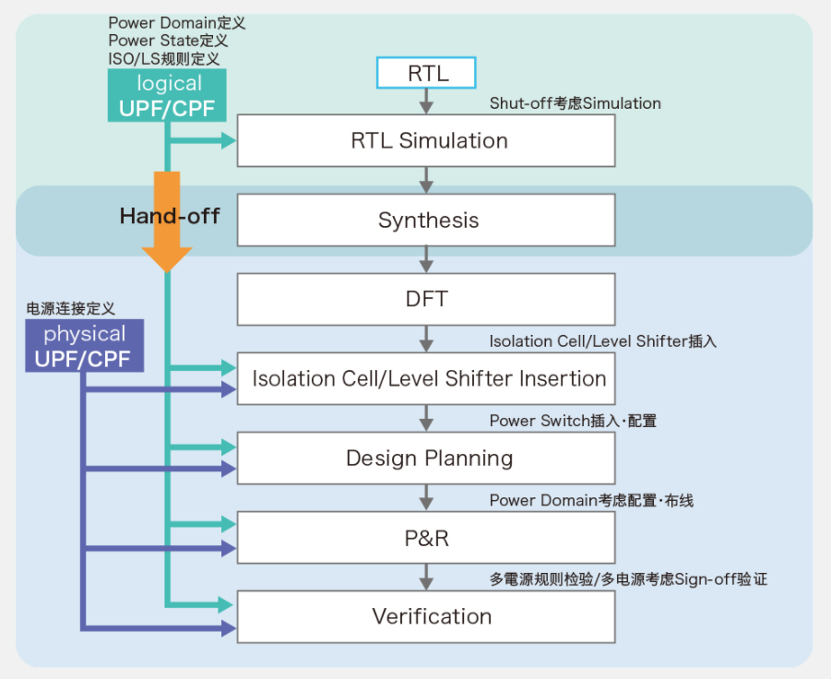

.png) 全面採用UPF/CPF的低功耗設計環境

全面採用UPF/CPF的低功耗設計環境

Socionext通過UPF*1及CPF*2對電源規格進行一貫管理,支援電力門控設計和多電源・多電壓設計,針對IP的增加使電源設計變得更加複雜,我們進行RTL模擬、多電源驗證及物理設計,提供整體解決方案。這個解決方案把電源規格分為邏輯規格和物理規格管理,通過定義邏輯規格,可進行RTL模擬的切斷電源驗證。把驗證的RTL和電源邏輯規格切換為物理設計,備有定義電源連接的電源的物理規格,基於這些電源規格(UPF/CPF)進行物理設計。按上述方式電源規格通過UPF/CPF進行管理,通過設計流程使用,明確電源規格,可進行高可靠性設計。

*1:UPF(Unified Power Format)是用來描述作為IEEE Std. 1801IEEE Std. 1801標準化的低功耗設計指標的標準規格 (http://www.ieee.org/)。

*2:CPF(Common Power Format) 是用來描述已在Si 2標準化的低功耗設計指南的標準規格 (http://www.si2.org/?page=811)。

[全面採用UPF/CPF的低功耗設計環境]

聯絡我們

聯絡我們